## Ph.D Thesis

# A study on improving the performance of three-stage Clos networks

# Labson Koloko

Graduate School of Engineering Science, Department of Mathematical Science and Electrical-Electronic-Computer Engineering, Akita University

This dissertation is submitted in partial fulfilment for the award of the degree of Doctor of Engineering in Electrical and Electronic Engineering

September 2021

# Dedication

This thesis is dedicated to my mum whose prayers and faith inspires me to move to higher heights. To my late Dad who taught me to always work hard and be resilient in life.

# Personal quote

"Never let disappointment make you drop God's promises for your life"

# Declaration

This dissertation is the result of my own work and does not include anything which is the outcome of work done in collaboration except where specified within the text. It has not been submitted in part or in whole to any university or institution for any degree or qualification.

Signed .....

Date .....

2021 Akita University.

# List of Publications

This dissertation is based on my published international journal and conference papers.

### International Journal papers

1. L. Koloko, T. Matsumoto and H. Obara, "Design and implementation of fast and hardware-efficient parallel processing elements to set full and partial permutations in Beneš networks," *IET Journal of Engineering*, 2021.4, Doi: 10.1049/tje2.12037.

2. L. Koloko, H. Obara and S.Kumagai, "Structure and non-blocking properties of bidirectional unfolded two-stage switches," *Electronics Letters*, 2021.6, doi:10.1049/ell2.12258.

3. L. Koloko, 小原仁, "3段Clos 網のルーチング制御の高速化に向けたFPGAによる非同期並列処理回路の試作,"電子情報通信学会論文誌B, Vol. J104–B, No. 7, pp. 598–602, 2021, doi: 10.14923/transcomj.2020BLL0002

4. L. Koloko and H. Obara, "Applying bidirectional crossbar switches with extra sets of inlets and outlets to three-stage Clos networks," *International Journal of Energy, Information and Communications*, Accepted under publication.

### **International Conference Papers**

1. L. Koloko, N. Takanohashi, Y. Katoh, P. Selin and H. Obara, "Network utilization monitoring technique using probe packet delay variance," *Proceedings of International Conference on Electrical Engineering*, G5-0930, Seoul, Korea, June 24-28, 2018.

2. L. Koloko and H. Obara, "Nonblocking Properties of three-stage Clos Networks Composed of crossbar switch elements with an Extra set of Inputs and Outputs," *The 9th International Conference on Electronics, Communications and Networks (CECNet 2019)*, CNT2476, Kitakyushu, Japan.Oct. 18-21,2019.

3. L. Koloko and H. Obara, "Nonblocking Properties of 3-stage Clos networks comprised of unidirectional crossbars," *Proceedings of 25th OptoElectronics and Communications Conference (OECC2020)*, pp.1-3 (doi:10.1109/OECC48412.2020.9273703), Taipei, Taiwan, October 4-8, 2020.

4. L. Koloko, T. Matsumoto and H. Obara, "FPGA implementation of parallel routing algorithm for three-stage Clos networks with component switch sizes of a power of two," *Proceedings of International Conference on Emerging Technologies for Communications*, D2-1, Tokyo, Japan (Virtual Conference), December 2-4, 2020

紀要(査読あり)

1.小原 仁, Koloko Labson, "3段Closスイッチ網の性能改善に関する研究(その1) -研究の背景とスコープー,"秋田大学大学院理工学研究科研究報告,第39号, pp.9-14, 2018

国内大会講演研究会(査読なし)

2. 中川原 敬佑, Labson Koloko, 加藤 陽介, 小原 仁, "3段Closスイッチ網の性能改善に関する研究(その2) - 空きポートを利用した双方向クロスバースイッチの構成-," 電気関係学会東北支部連合大会講演論文集, p.112, 2018

3. 柳 晋登, Labson Koloko, 加藤 陽介, 小原 仁, "3段Closスイッチ網の性能改善に 関する研究(その3) - FPGAを用いたハードウェア処理による3段Clos網の高速制 御-," 電気関係学会東北支部連合大会講演論文集, p.112, 2018.

4. Labson Koloko, 橋本 拓大, 加藤 陽介, 小原 仁, "Improving Performances of Three-Stage Clos Networks, Part IV," 電気関係学会東北支部連合大会講演論文集, p.119, 2018.

5. 渋谷 悠悟, Labson Koloko, 加藤 陽介, 小原 仁, "3段Closスイッチ網の性能改善に関する研究(その5) -3段Closスイッチ網の並列制御方式の提案-," 信学技報, vol.118, no.232, pp.1-5, 2018.

6. 松本崇寛大, Labson Koloko,加藤 陽介, 小原 仁, "Benes網の並列ハードウェア 制御回路の高速化,"電気関係学会東北支部連合大会講演論文集, 2B07, 2019.

7. プトリナディラビンティアズマン, Labson Koloko,加藤 陽介,小原 仁, "3段Clos網のノンブロック性能評価のためのシミュレーション条件の最適化,"電気関係学会東北支部連合大会講演論文集,2B08,2019.

8. 柳 晋登, Labson Koloko,加藤 陽介, 小原 仁, "並列ハードウェア制御による3段Closスイッチ網の高速制御," 電気関係学会東北支部連合大会講演論文集, 2B09, 2019.

9. 松本崇寛,野中翔太,Labson Koloko,加藤 陽介,小原 仁, "3段Clos網の並列 ハードウェア制御アルゴリズムの提案," 電気関係学会東北支部連合大会講演論 文集, P05, 2020. Akita University

This page is left blank intentionally

#### Abstract

## A study on improving the performances of three-stage Clos networks

### Labson Koloko

#### Abstract

With the increase in demand for IP (internet protocol) traffic on the internet and many communication networks in recent past, high-capacity and fast switching routers and switches have become essential in the backbone of communication networks. Routers and switches play a very important role of routing signals from one node to another in a network. Their capacity and the speed at which this is performed are key to achieving the desired performances in current communication networks. Most of the routers and switches are constructed with a multistage switching fabric at the core of its switching. The three stage Clos network and the Benes networks are such multi-staged switching fabrics. Multi-staged switches are organized in such a way that several smaller switches in one stage are connected to other switches in another stage to form a network with larger capacity. Each switch in each stage connects to every switch in the next stage. Multi staging helps solve the scalability problem that comes with the crossbar switch. Using a single crossbar switch as a switching fabric does not allow for scalability as the cross point increases exponentially with an increase in the number of ports. The three stage Clos network, usually denoted by C(n, m, r), where n, m and r represent the number of inputs/output ports of the input/output switches, the number of middle stage switches and the number of inputs/output switches respectively, has been one of the most widely used designs in many switching architectures. This thesis discusses two approaches in improving the performances of the switch. Firstly, the study considers the structure of Clos networks that include conventional crossbar switch elements which are composed of  $2 \times 2$  basic switching elements often used in optical switches. The study highlights the fact that crossbar elements have a number of idle ports unused and discuss how these idle ports can be used to improve the non-blocking properties of the network. An elaboration on the nonblocking properties of this network is provided. This work shows that the lower bound on the value of m for rearrangeably non-blocking switches can be reduced by 25% of the original clos network when idle ports are used. It has also been demonstrated in this study that when m = n, the number of rearrangements is reduced to 1 regardless of the values of n and r. Typical conventional Clos switches require r-1 rearrangements in a worst-case scenario. The work also shows that the number of middle stage switches required for wide sense non-blocking in the Clos network can be reduced approximately by 25% lower than the conventional Clos switch. Secondly, this work discusses the design and implementation of fast and hardware-efficient parallel processing elements to set full and partial permutations in Benes network. A new design of parallel and distributed processing elements for configuring Benes network is proposed. The novel parallel algorithm can realize full and partial permutations in a unified manner with very little overhead time and extra hardware. The proposed design reduces the hardware complexity of processor elements from  $O(N^2)$  to  $O(N(\log_2 N)^2)$  due to the distributed architecture. The distributed architecture also allows for pipelining in the architecture which in turn reduces the time complexity of processor elements from  $O((\log_2 N)^2)$  to

$O(\log_2 N)$ . To further reduce the time complexity, asynchronous operation was introduced in part. The prototype is implemented in a field programmable gate array and the performance is investigated for the switch size of N = 4 to 32. Further a fast parallel algorithm for setting up a three stage clos network in which the component switch sizes have a power of two is presented. The algorithm is also implemented in hardware using field programmable logic gate array and its performance investigated through experiments. This work reports that the algorithm can operate as fast as the time complexity of  $O(\log_2 N)$  up to a certain switch size, in contrast to the conventional algorithms which require a time complexity of at least  $O((\log_2 N)^2)$ . The experimental results demonstrate that the proposed designs outperform recent methods several times in terms of hardware and processing complexities.

# Acknowledgements

First of all, I thank God for giving me the breath of life and for the good health I have enjoyed throughout my studies.

I am greatly indebted to my supervisor, Professor Hitoshi Obara for accepting me into his laboratory and for allowing me to carry out research under his supervision in the field of internet networks and Optical communication systems. My whole period of research under his guidance has been very rewarding. He has taught me how to do research. Approaching research problems in a piecewise manner, presenting research results, writing papers and how to give seminars. I have learnt a lot of things from him including his passion for research, being hardworking and his patience and kindness towards students. He made time to listen to me and discuss his ideas with me whenever I asked. He has always been encouraging and pushing me to work extra hard and never to give up. He has been more than a usual supervisor can be. His influence on me is far beyond. I am very fortunate and proud to have been his student. I cannot thank him enough! I remain indebted to him the rest of my life.

I owe my special thanks to professor Kumagai the head of Department who took me up as his student and Professor Motoshi Tanaka who allowed me to be part of his research laboratory after my supervisor retired.

Special thanks go to the other members of the supervisory committee, Professor Saitou and Professor Yamaguchi. They provided not only useful comments but they sparked numerous discussions that helped me understand my subject even better.

I am very grateful to Mr. Yosuke Kato who was always available to help me setup experiments and provisioning all the necessary equipment and tools needed in my research.

I am grateful to all the members of the Obara laboratory who made life easier and provided an enjoyable friendly working atmosphere in the laboratory.

I am grateful to my mum for her prayers and never ending encouragements, my brothers and sisters for their support and who continuously cheered me to push on.

Finally, I would like to thank the Japanese government for offering me the MEXT scholarship to come and study in Japan. I thank all members of the Electrical Engineering department, the staff, faculty members and fellow students who made the department a great place to work and study. My years at Akita University were very enjoyable.

# Contents

| Dedication                 | i    |

|----------------------------|------|

| Personal quote             | ii   |

| Declaration                | iii  |

| List of Publications       | iv   |

| blank page                 | vi   |

| Abstract                   | vii  |

| Acknowledgements           | ix   |

| Contents                   | xii  |

| List of tables             | xiii |

| List of Figures            | xvi  |

| Abbreviations and Acronyms | xvii |

## Chapter 1

| Intr | Introduction 1         |   |  |

|------|------------------------|---|--|

| 1.1  | Background             | 1 |  |

| 1.2  | Switching fabrics      | 3 |  |

| 1.3  | Multi-staged Switches  | 4 |  |

| 1.4  | Control algorithms     | 6 |  |

| 1.5  | Outline of this thesis | 8 |  |

## Akita University

## Chapter 2

| Rel | Related works/Literature review 9 |                                             | 9  |

|-----|-----------------------------------|---------------------------------------------|----|

| 2.1 | Previo                            | ous clos structure and properties           | 9  |

|     | 2.1.1                             | Summary of Contribution                     | 10 |

| 2.2 | Recen                             | t Benes and clos routing control algorithms | 11 |

|     | 2.2.1                             | Control algorithm in BNW                    | 11 |

|     | 2.2.2                             | Summary of contributions                    | 12 |

|     | 2.2.3                             | Control algorithms in TSCN                  | 12 |

|     | 2.2.4                             | Summary of contributions                    | 13 |

### Chapter 3

| Design and operation of the proposed structure 14 |                              | 14 |

|---------------------------------------------------|------------------------------|----|

| 3.1                                               | Crossbar modification        | 14 |

| 3.2                                               | Application of XBS to TSCN   | 15 |

|                                                   | 3.2.1 Bidirectional TSCN     | 15 |

| 3.3                                               | Proposed Unidirectional TSCN | 21 |

| 3.4                                               | Wide-sense non blocking      | 22 |

### Chapter 4

| Simulation setup and experimental results 24 |                                       |    |

|----------------------------------------------|---------------------------------------|----|

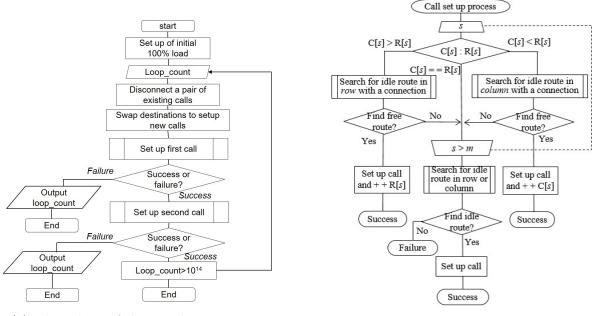

| 4.1                                          | Simulation flow in Bidirectional TSCN | 25 |

| 4.2                                          | Simulation and experimental results   | 29 |

| 4.3                                          | Summary                               | 33 |

## Chapter 5

Structure and non-blocking properties bidirectional two stage switches 35

## Akita University

| 5.1 | Brief introduction                      | 35 |

|-----|-----------------------------------------|----|

| 5.2 | Proposed structure of UTSN              | 35 |

| 5.3 | Non-blocking properties of $B(n, m, r)$ | 36 |

| 5.4 | Hardware complexity of $B(n, m, r)$     | 38 |

| 5.5 | Summary                                 | 39 |

## Chapter 6

| Des | Design of parallel control algorithm 40                    |                                                                                                 |    |

|-----|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----|

| 6.1 | Benes Network                                              |                                                                                                 |    |

| 6.2 | Design                                                     | of parallel processing elements                                                                 | 45 |

|     | 6.2.1                                                      | Design overview                                                                                 | 45 |

|     | 6.2.2                                                      | Design of PEs for Full permutation                                                              | 46 |

|     | 6.2.3                                                      | Design for partial permutations Unified Parallel algorithm for full<br>and partial permutations | 50 |

| 6.3 | 6.3 FPGA Design and Experimental Results for Benes network |                                                                                                 | 52 |

|     | 6.3.1                                                      | Design environment                                                                              | 52 |

|     | 6.3.2                                                      | Experimental results and discussion                                                             | 52 |

|     | 6.3.3                                                      | Summary                                                                                         | 56 |

| 6.4 | Clos N                                                     | fetworks                                                                                        | 57 |

|     | 6.4.1                                                      | Outline of the proposed routing algorithm in TSCN                                               | 57 |

|     | 6.4.2                                                      | Hardware Implementation of the proposed algorithm $\ldots \ldots \ldots$                        | 58 |

|     | 6.4.3                                                      | FPGA design and experimental results                                                            | 63 |

|     | 6.4.4                                                      | Summary                                                                                         | 64 |

## Chapter 7

Conclusion and Future works

65

# List of Tables

| 1 | Summary of the Properties of the TSCN                                                              | 5  |

|---|----------------------------------------------------------------------------------------------------|----|

| 2 | Summary of switch performances for conventional and proposed unidirectional and bidirectional TSCN | 33 |

| 3 | Summary of the performance of the algorithm                                                        | 56 |

# List of Figures

| 1  | Role of a switching function in telephony networks                                                                          | 1  |

|----|-----------------------------------------------------------------------------------------------------------------------------|----|

| 2  | General architecture of a switching node                                                                                    | 2  |

| 3  | Single stage architecture of the XBS with BSE                                                                               | 3  |

| 4  | Multi staged architecture of XBS                                                                                            | 4  |

| 5  | An $N \times N$ three stage Clos network represented by $C(n,m,r)$                                                          | 5  |

| 6  | Strictly non-blocking condition for a worst case scenario with minimum number of middle stage switches required             | 6  |

| 7  | Recursive construction of the Benes network                                                                                 | 7  |

| 8  | Sequential route setup in the TSCN                                                                                          | 7  |

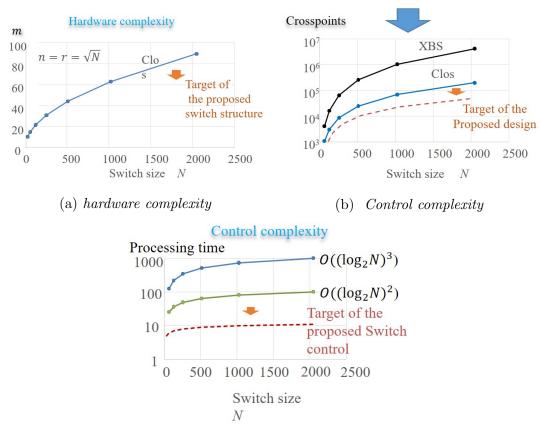

| 9  | Summary of objectives of proposed target (a) Hardware complexity (b) crosspoint complexity reduction (c) Control complexity | 11 |

| 10 | Conventional crossbar (XBS) Switch with idle ports                                                                          | 14 |

| 11 | Two possible types of XBS modification (a) Unidirectional modified (b) bidirectionally modified                             | 15 |

| 12 | Two possible types of XBS modification                                                                                      | 16 |

| 13 | Special configuration with $m = n$ middle stage switches $\ldots \ldots \ldots$                                             | 17 |

| 14 | Column Blocking and blocking resolution                                                                                     | 18 |

| 15 | bidirectional modified TSCN with $1^{st}$ and $3^{rd}$ stage modified                                                       | 19 |

| 16 | Sharing of rows and columns by a pair of connections in $XBS$                                                               | 19 |

| 17 | Routing $n$ calls using $m < n$ middle stage switches                                                                       | 20 |

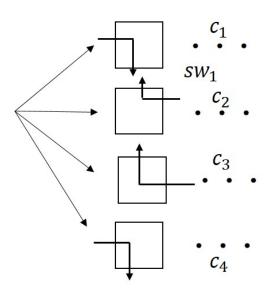

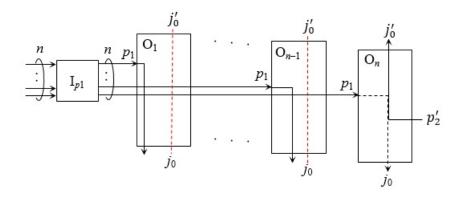

| 18 | Proposed Unidirectional TSCN                                                                                                | 21 |

| 19 | Derivation of the proposed lower limit                                                                                      | 23 |

| 20 | Flow chart of the simulation process                                                                                        | 24 |

| 21 | Simulation of the XBS in C programing                                                                                       | 25 |

| 22 | Initializing the XBS to idle state                                                                                          | 26 |

| 23 | Simulation of the XBS in C programing                                                                                       | 26 |

| 24 | Disconnection of a random pair in an XBS                                                                                    | 27 |

# Akita University

| 25 | Initializing the XBS to idle state                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 26 | Simulation results of the conventional Clos network $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                           | 28 |

| 27 | Simulation results of the proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                             | 29 |

| 28 | Worst case blocking and need to rearrangement                                                                                                                                                                                                                                                                                                                                                                                                                               | 30 |

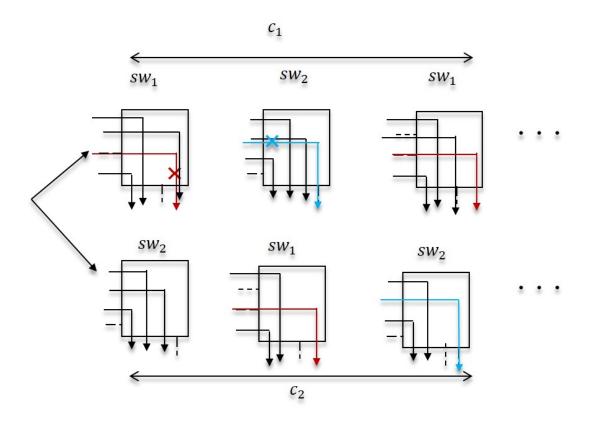

| 29 | Rearrangement process in conventional TSCN                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31 |

| 30 | Rearrangement process in proposed architecture                                                                                                                                                                                                                                                                                                                                                                                                                              | 32 |

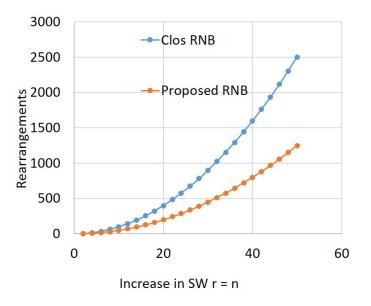

| 31 | comparison of the number of rearrangements in conventional and proposed architecture                                                                                                                                                                                                                                                                                                                                                                                        | 32 |

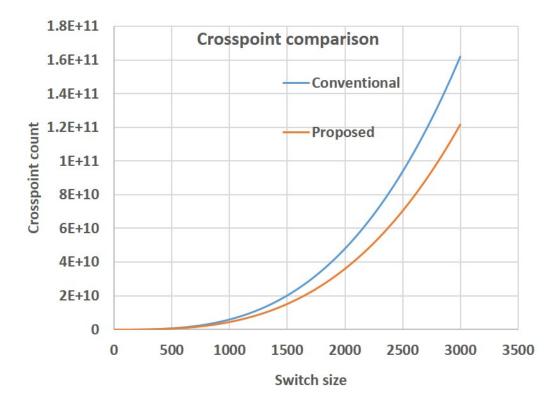

| 32 | Cross point comparison in conventional and proposed architecture $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                   | 34 |

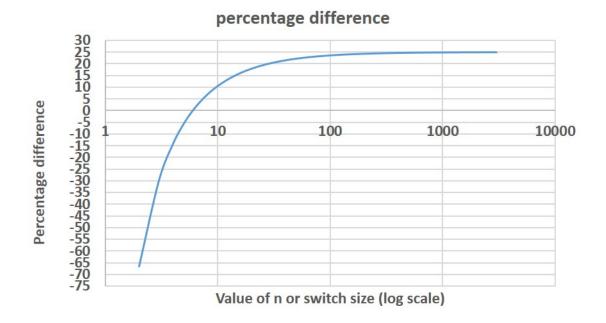

| 33 | Overall percentage reduction in the number of middle stage switches required                                                                                                                                                                                                                                                                                                                                                                                                | 34 |

| 34 | Structure of $B(n, m, r)$                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36 |

| 35 | Design Example of ISM using bidirectional switching                                                                                                                                                                                                                                                                                                                                                                                                                         | 36 |

| 36 | Design Example of OSM using bidirectional switching                                                                                                                                                                                                                                                                                                                                                                                                                         | 37 |

| 37 | Worst-case scenario for rearrangement in $B(n, n, r)$                                                                                                                                                                                                                                                                                                                                                                                                                       | 37 |

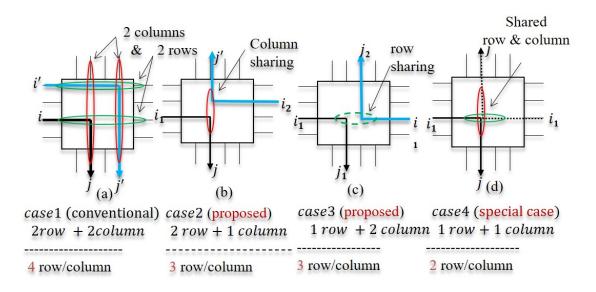

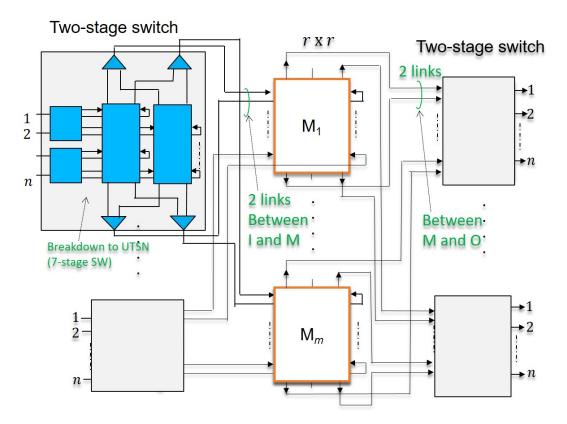

| 38 | Modified TSCN with first and third stages replaced by two-stage switches                                                                                                                                                                                                                                                                                                                                                                                                    | 39 |

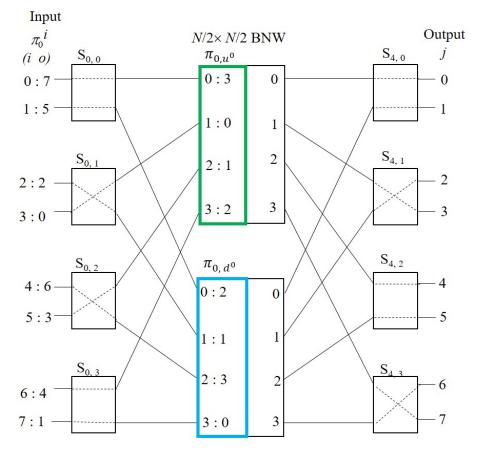

| 39 | Primitive three-stage structure of $N \times N BNW (N = 8) \dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                               | 41 |

| 40 | Full picture of $N \times N$ BNW ( $N = 8$ )                                                                                                                                                                                                                                                                                                                                                                                                                                | 42 |

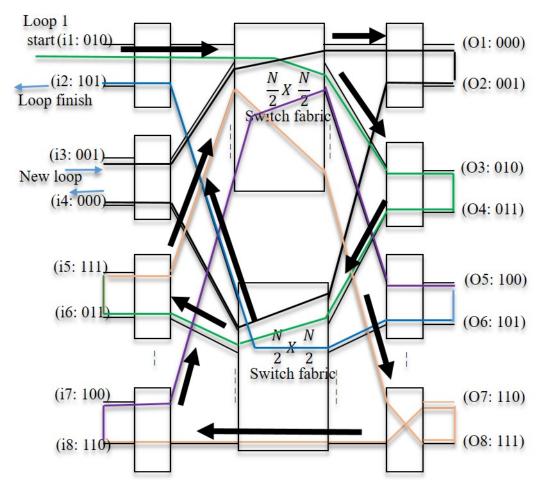

| 41 | Conventional looping algorithm in Benes network                                                                                                                                                                                                                                                                                                                                                                                                                             | 43 |

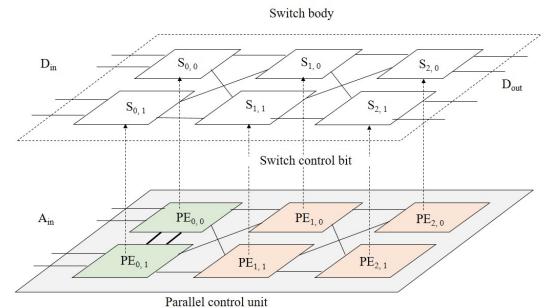

| 42 | Proposed Design overview of the parallel control unit with the switch body                                                                                                                                                                                                                                                                                                                                                                                                  | 45 |

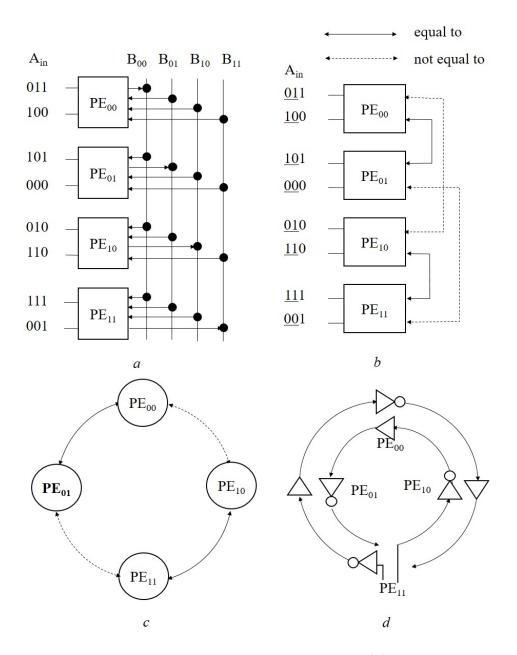

| 43 | Bus-connected PE array and its operation: (a) each PE accepts address<br>information and interchanges switch control data via multiple buses in<br>parallel; (b) link status after first phase; (c) link diagram in a cycle; (d)<br>implementing link diagram in FPGA using inverting and non-inverting<br>gates                                                                                                                                                            | 47 |

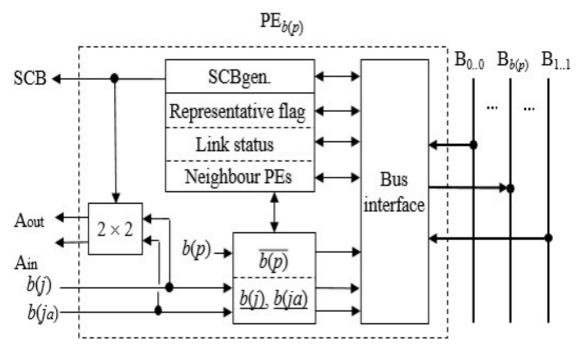

| 44 | Simplified functional diagram of PE with binary suffix $b(p)$                                                                                                                                                                                                                                                                                                                                                                                                               | 48 |

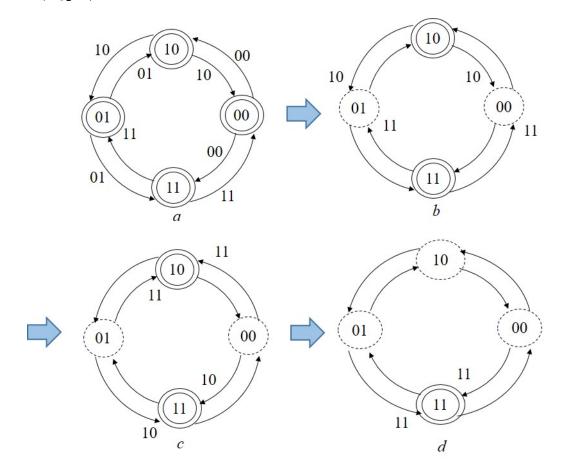

| 45 | Iterative steps to determine representative PE in the second phase: (a) each PE is eligible for representative in the initial state; (b) the PE receives two suffixes and compares its suffix to them and surviving PEs are reduced to one-half and lost PEs become transparent and bypass incoming data; (c) the competition process is repeated in subsequent iterations; (d) maximum suffixes return to the originating PE in the final iteration $\ldots \ldots \ldots$ | 49 |

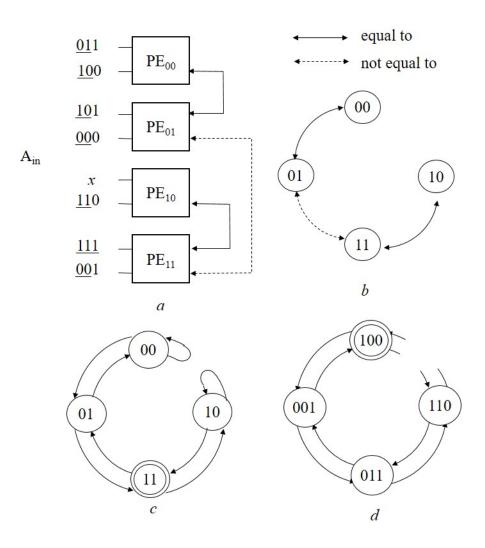

| 46 | Example of partial permutation and modified link diagrams against dis-<br>connection: (a) input address 010 in Fig. 42 a becomes idle and is repre-<br>sented as x; (b) the link diagram is disconnected between $PE_{00}$ and $PE_{10}$ ;<br>(c) the disconnection is protected by the loop-back mechanism (similar to<br>self-healing ring networks); (d) alternatively, each PE is provided with an |    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | extended suffix to mask disconnection                                                                                                                                                                                                                                                                                                                                                                  | 51 |

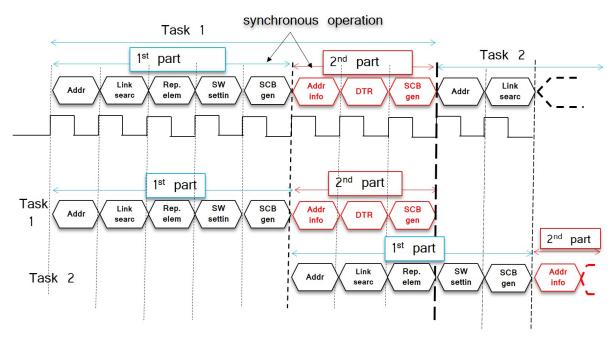

| 47 | Asynchronous operation of the proposed structure $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                         | 53 |

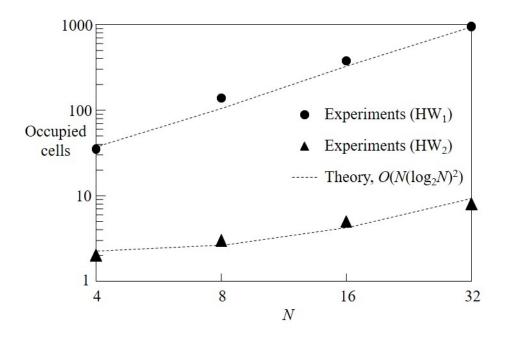

| 48 | Number of occupied slices in FPGA vs. switch size                                                                                                                                                                                                                                                                                                                                                      | 53 |

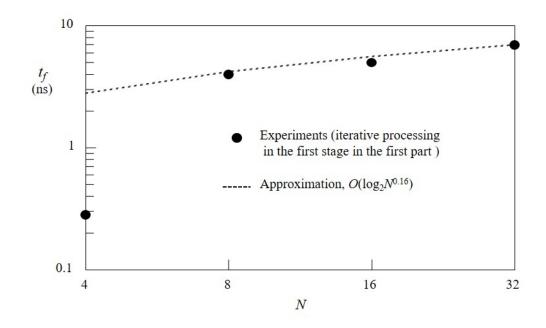

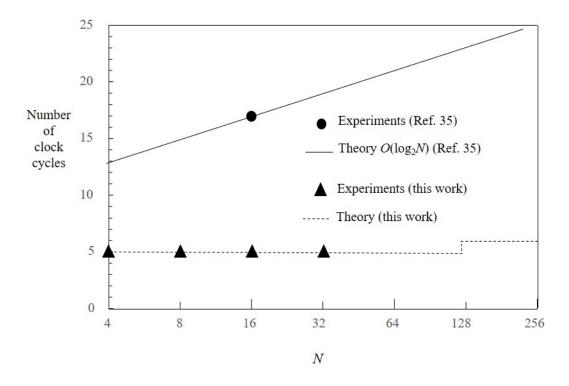

| 49 | Processing time $t_f$ vs. switch size N for the first part in the proposed design                                                                                                                                                                                                                                                                                                                      | 54 |

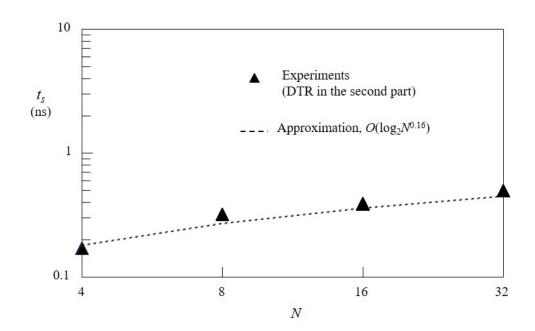

| 50 | Processing time $(t_s)$ vs.switch size N for the Second part $(DTR)$ in the proposed design                                                                                                                                                                                                                                                                                                            | 55 |

| 51 | Total clock cycles vs. switch size for the first stage in the first part                                                                                                                                                                                                                                                                                                                               | 55 |

| 52 | Three stage Clos network $C(4, 4, 2)$                                                                                                                                                                                                                                                                                                                                                                  | 57 |

| 53 | Proposed routing principle with iterations                                                                                                                                                                                                                                                                                                                                                             | 58 |

| 54 | Routing principle with iterations of the proposed algorithm $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                     | 59 |

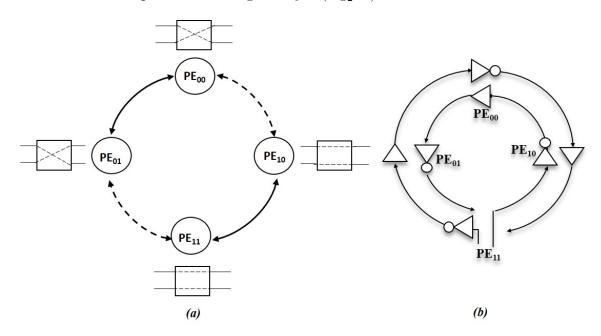

| 55 | Arrangement and operation of parallel processing elements (a)PEs con-<br>nected to bus bars (b) Neighbour search establishment (c) Link relationship<br>status (d)Implementation of link status using Inverting and non inverting<br>gates                                                                                                                                                             | 60 |

| 56 | Iterative procedure for determining the representative PE                                                                                                                                                                                                                                                                                                                                              | 61 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                        | 01 |

| 57 | Determination of link status of each PE (a).Representative PE initially<br>setting its status to bar triggering the other PE status (b). The link status<br>implementation using inverting and non-inverting gates                                                                                                                                                                                     | 62 |

| 58 | Experimental processing time for the first part of the algorithm $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                     | 63 |

# List of Abbreviations and Acronyms

| BNW  | Benes network                        |

|------|--------------------------------------|

| BSE  | Basic switching element              |

| FPGA | Field programmable gate array        |

| IP   | Internet protocol                    |

| MIN  | Multi staged interconnecting network |

| PE   | Processor elements                   |

| PCU  | Parallel control unit                |

| RNB  | Rearrangeably non blocking           |

| SCB  | Switch control bit                   |

| SE   | Switching element                    |

| SNB  | Strictly non blocking                |

| SW   | Switch                               |

| TSCN | Three stage Clos network             |

| UTSN | Unfolded Two stage network           |

| WSNB | Wide sense non blocking              |

| XBS  | Crossbar switches                    |

| NoC  | Network on Chip                      |

|      |                                      |

## Chapter 1

## Introduction

### 1.1 Background

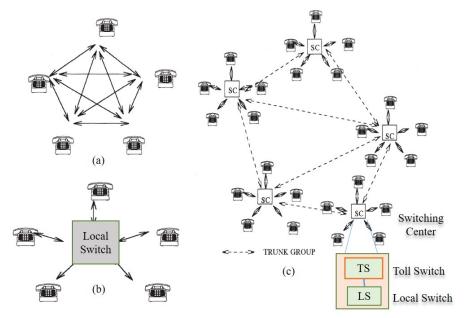

Recently, the internet and many communication networks have experienced an exponential rise in the demand for internet protocol (IP) traffic as predicted by the cisco report [1]. This rise in demand is as a result of an increase in real-time services. With this increase in traffic, high-capacity, fast switching routers and switches are needed in backbone communication switching networks. Switching is an important component of any telecommunication system. In a telecommunication system, a switching system provides a means to pass information from one node to another node in a network and therefore is core to any communication system. For example, in earlier days of telephony networks, the role of the switching function was performed by a pair of cables that connected two terminals that needed to connect to each other. As can be seen in fig. 1(a) each terminal had to be connected to another terminal through a single transmission line. As the number of terminals increased to N, we see that the number of links increased as N(N-1)/2. This was not viable because these links remained idle most of the time and were only used during a short period of time when a call was generated, hence a central switch was introduced and each terminal only needed a pair of connections to it (figure 1(b)). These local switches were connected to toll switches that enable long distance communications (see figure 1(c))[2].

Source: "Switching and Traffic Theory for integrated Broadband Networks," by J. Hui, Springer US 1990.

#### Figure 1: Role of a switching function in telephony networks

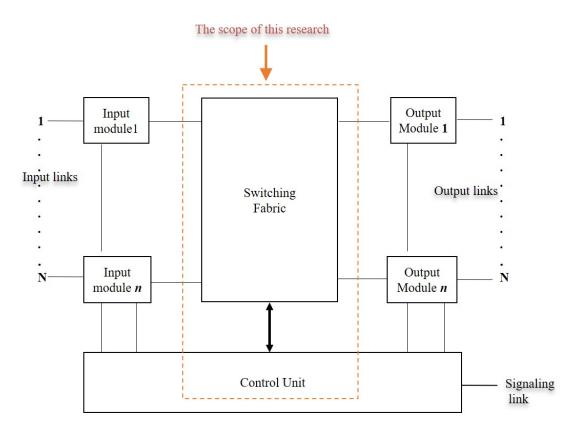

The general architecture of a switching node is shown in figure 2. A switching system

basically receives signals such as control signals, message signals and forwards them to a desired destination through a central module known as a *switching fabric*. These switch modules are controlled by a control unit that processes signaling links. (see figure 2).

Figure 2: General architecture of a switching node

In order to meet high capacity and fast switching, lots of research has been devoted to the design and implementation of the switching techniques [3]. Switching has evolved over many years since Charles Clos initiated his classical circuit switching theory in 1953 [2]. An increasing trend towards mega data centers in which the switching architecture proposed by Clos are used has been observed and this has been necessitated in order to support the ever increasing demand for data [4]. The growth in communication brought about the need for interconnecting many transmission links. This was because traffic on these links needed to be multiplexed onto fewer links going to the same location for effective utilization of resources. Secondly, the traffic on these links needed to be demultiplexed to different transmission links going to different locations. A space switch was a candidate for interconnecting such links [2]. A space division switch can be implemented by either an electromechanical or electronic switch. Prior to the advent of time division switching, all telephone and telegraph switching machines were implemented using a variety of space division switching techniques, particularly Strowger (step-by-step) switches and crossbar switches [5].

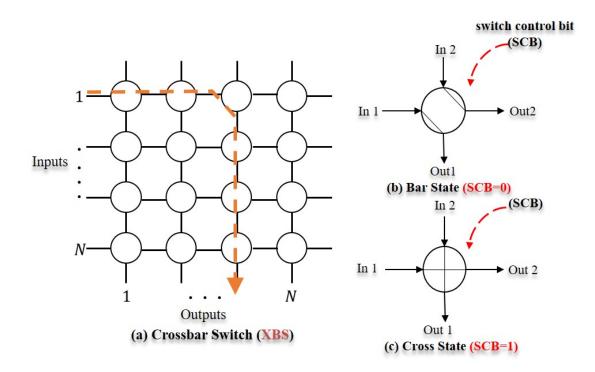

### **1.2** Switching fabrics

At the core of any switch, is a switching fabric. The switching fabric is made up of basic switching elements (BSE) arranged in a regular and planar structure forming what is known as a crossbar switch (XBS) as shown in figure 3(a). BSEs have two input ports and two output ports. Each BSE can be in either of the two states at a given time; cross state with a switch control bit (SCB) of 1 (figure 3(b)) or bar state with an SCB of 0 (figure 3(c)), hence the name XBS. In the bar state, inputs port 1 and port 2 connects with outputs port 1 and port 2 respectively. This means that the BSE forwards its two input signals from the input ports straight to the two opposite output ports (figure 3 (a)). In cross state, input port 1 connects with output port 2 and input port 2 connects with output port 1 (see figure 3 (b)). BSE are arranged in a square matrix configuration to form larger crossbar switches with multiple inputs n and multiple outputs m [2]. When m > n, the XBS becomes a rectangular switch and if n = m, the switch is a square XBS. The XBS in figure 3(c) has n = m = N and is therefore an  $N \times N$  XBS.

Figure 3: Single stage architecture of the XBS with BSE

The XBS takes its inputs and connects them to any of the m outputs. XBSs are represented as  $n \times m$  where n is the number of input ports and m is the number of output ports (figure 3(a)). An XBS is considered to be strictly non-blocking (SNB) switches, meaning that any signal at any input port can be transferred to any output port without colliding or blocking with any existing signals in the switch and its control is very simple. A switching fabric is said to be blocking if there are path assignments which cannot be realized in the switching network. With an increase in the number of ports, the XBS becomes impractical to implement because the cross point requirement increases as nmand when n = m = N, then the cross point count becomes  $N^2$ .

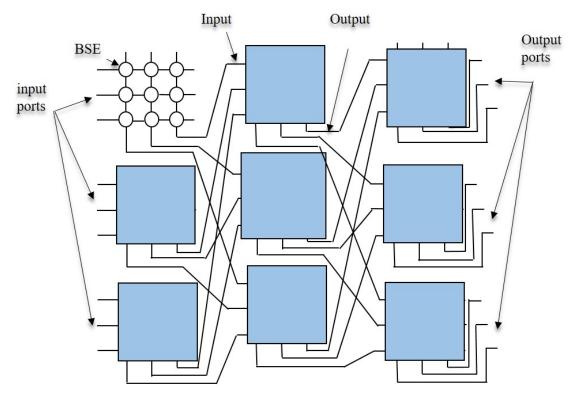

### 1.3 Multi-staged Switches

During switching in an XBS, a single cross point in a row or a column is activated. To route a group of signals, several cross points are activated in an XBS. When several XBSs are connected between each other to form larger switches, such switches are referred to as multi-staged switching fabrics. XBSs are multi-staged to provide more routes at a reduced cross point count. Multi-staging has proved to be a good solution to the scalability issue of the XBS and has helped build large switching architectures using small BSEs (see figure 4). These play an important role in any switching devices such as routers and switches. Multistage interconnection networks (MIN) are used in building larger IP routers with higher capacities.

Figure 4: Multi staged architecture of XBS

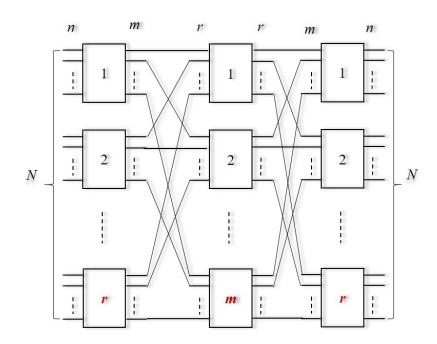

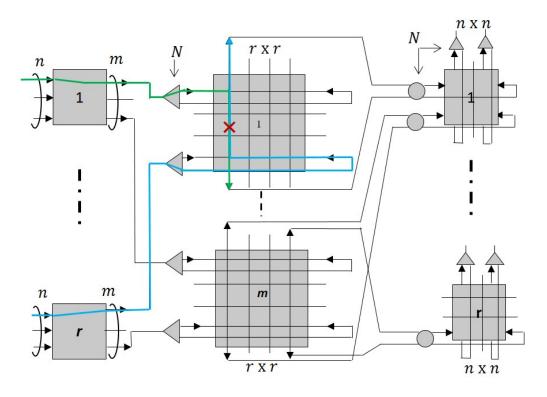

Charles Clos in 1953 proposed a three stage network which is now known as a Three Stage Clos network (TSCN). The TSCN consists of  $r, n \times m$  XBS in the first stage connected to each  $m, r \times r$  XBS in the second stage. Each m XBS in the second stage is connected to a set of  $r, m \times n$  XBSs in the third stage. A TSCN C(n, m, r) shown in figure 5 is made up of three stages, where n is the number of input ports and output ports in the first and third stage XBSs respectively. m is the number of middle stage XBSs and r is the number of input/output XBSs in the first and third stages. Each of the first stage XBS is connected to the XBSs in the second stage only through a single link. Similarly, each of the second stage XBSs is connected to each of the third stage XBS through a single link. A multi-staged switch scales better than the XBS. An  $N \times N$  TSCN has a much lesser cross point count of  $N^{1.5}$  than the  $N^2$  cross point count in a single  $N \times N$  XBS [2].

The TSCN has some important properties that make it to be widely used in many

Figure 5: An  $N \times N$  three stage Clos network represented by C(n, m, r)

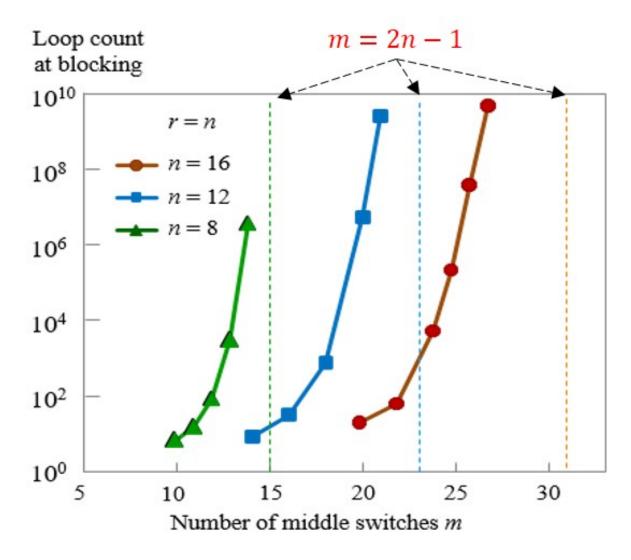

communication networks. These properties can be fine-tuned by properly setting the values of m and n. A summary of these properties and their values is provided in table 1 below. To obtain the SNB property, set  $m \ge 2n - 1$ . This is proven as follows; in a

| Number of<br>middle switches, m                                                                             | property                         |

|-------------------------------------------------------------------------------------------------------------|----------------------------------|

| m < n                                                                                                       | Blocking                         |

| $m \ge n$                                                                                                   | Rearrangeably non-blocking (RNB) |

| $ \begin{array}{c} m \ge \lfloor 2n - n/F_{2r-1} \rfloor \\ F_k : k - th \ Fibonacci \ number \end{array} $ | Wide-sense non-blocking (WSNB)   |

| $m \ge 2n - 1$                                                                                              | Strictly non-blocking (SNB)      |

Table 1: Summary of the Properties of the TSCN

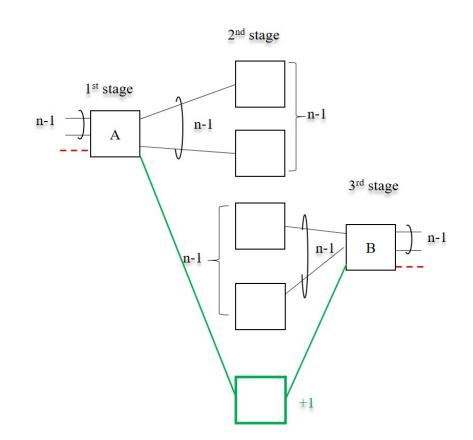

worst case scenario, if a free port exists at the input port of an input XBS A, we have n-1 existing connections that correspond to a set of unreachable number of middle stage switches. Similarly, a free output port exists at the output XBS B, we have the other n-1 connections connected through another set of n-1 unreachable middle stage switches. To provide a free connection path, Clos showed that an extra middle stage switch (shown in green in figure 6) must be added, hence there must be at least 2(n-1)+1 middle stage switches. When  $m \ge n$  the TSCN becomes RNB. A TSCN can also be wide sense non-blocking (WSNB) if a route can be provided in a network but some rule must be used when setting up a path otherwise blocking may occur later. If the number of middle stage switches is less than n the switch is referred to as a blocking switch since some connection paths cannot be provided in the switch.

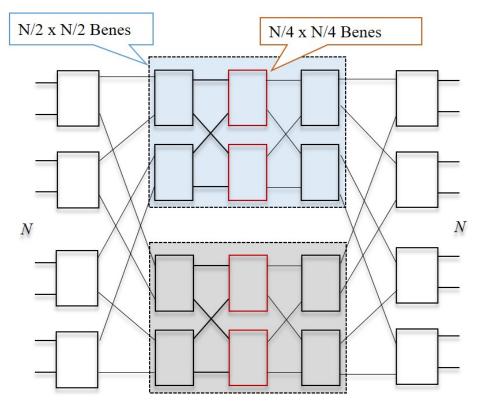

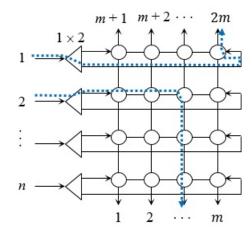

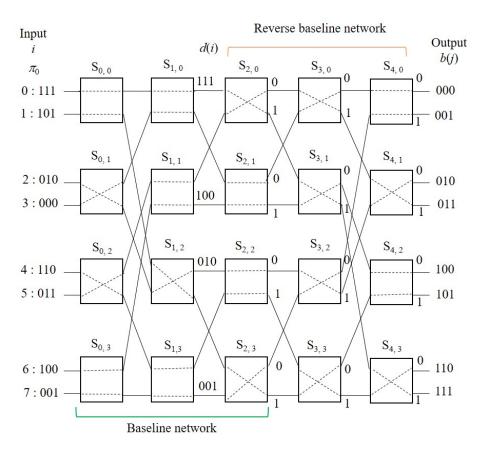

Another multistage switching network is the Benes network (BNW). It is a special type of TSCN with m = n = 2 and is composed of  $2 \times 2$  BSEs as building blocks. It has  $2 \log_2 N - 1$  stages of which each is made up of  $N/2 \ 2 \ \times 2$  switches. The number of inputs and outputs is given by  $N = r \times r = 2^n$ . The central stage is composed of two

Figure 6: Strictly non-blocking condition for a worst case scenario with minimum number of middle stage switches required

$N/2 \times N/2$ . Each of the  $N/2 \times N/2$  switches are made up of  $\log_2 N - 1.2 \times 2$  BSE (see Fig. 7). In the case where N = 4, the middle stage switch is composed of 2.2  $\times$  2 BSE. When N is increased, the center stage can be repeatedly replaced by  $N/2 \times N/2$  to form a rearrangeably non-blocking (RNB) switch. The total number of switching elements required is  $N \log_2 N - N/2$ .

In an RNB switch, a new path can always be set up between an existing free input port to an existing free output port but already setup paths must be rerouted to accommodate the new path.

Benes and Clos switches with 5,7,9, or more stages can be realized.

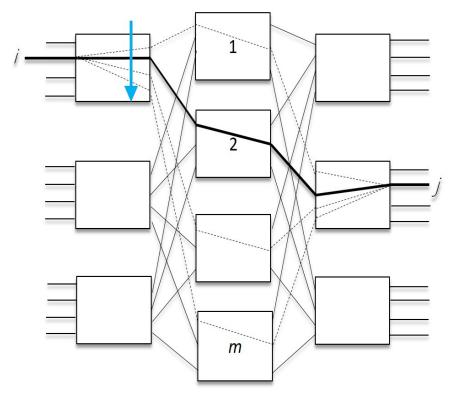

### 1.4 Control algorithms

In order to set up connection paths in non-blocking multistage switches, special routing algorithms are required. These are important because they determine the path setup time and the system reliability of the network which are important factors in determining the performance of a switching network. In setting up paths from an input i to and output j in the network, sequential search algorithm with complexity of O(m) per connection is used resulting in a total of O(Nm) for a switch size of inputs N as shown in figure 8. These sequential algorithms have long processing time. Therefore, parallel algorithms which have lower processing time have been introduced. It is a well known fact that

Figure 7: Recursive construction of the Benes network

parallel processing reduces the processing time of a given task [6]. This work seeks to improve the time for path setup in the Benes and Clos network.

Figure 8: Sequential route setup in the TSCN

## 1.5 Outline of this thesis

This dissertation is organized as follows; chapter 2 begins by reviewing the conventional structure and properties of the TSCN. It presents some related works that have been done in the area of structure and properties of three stage clos networks. It also covers the recent works done in routing control algorithms for Benes and Clos networks. Chapter 3 introduces the design and operation of our proposed Clos architecture. It introduces a new design in which conventional XBS are modified in two different ways and applied to designing the new TSCN architecture. The first is the unidirectional modified XBS and the second is the bidirectional modified XBS. Chapter 4 presents the simulation and experimental call setup in the new architecture. Performance results of the new proposed architectures are discussed and reported. Chapter 5 introduces a new emerging design principle options for relatively small-capacity switches. The non-blocking properties of unfolded two stage networks are discussed. In Chapter 6, the design of parallel control algorithms for the Benes and clos networks are presented. The design of parallel and distributed PEs for processing full and partial permutations in BNW is described. The hardware implementation of the algorithms performed on an FPGA to realize higher speed than the clock rate using asynchronous operation is also reported. Performances

of these algorithms are evaluated through experiments. Experimental results of the performances are highlighted in this section. Finally, chapter 7 concludes the dissertation and suggests future works.

## Chapter 2

## Related works/Literature review

### 2.1 Previous clos structure and properties

The clos architecture has been the most practical and cross point–efficient design principle for large switching networks [7]. It has been applied to various types of switches such as space switches [8], time division multiplexed switches [9], packet switches [10] and optical switches [11]. This is because of the non-blocking properties that the TSCN has. Clos networks were at the beginning invented for application in telephone exchange systems. However, recently it has been used in many applications ranging from electrical and optical cross connects which are essential for building communication networks that are economical with highly multiplexed signal links [12]. Clos networks have been classified based on their connecting capabilities. Some have been classified as strictly non-blocking (SNB) network [13], rearrangeably non-blocking (RNB) [14], wide sense non-blocking (WSNB) [15, 16, 17] and repackaged network [18]. In each of the classes, the relationship of the parameters n, m and r have been analyzed. By setting these parameters appropriately, the above properties of the clos network can be realized. The SNB network can be obtained when m is set equal to 2n-1. This means that any connection request can be established from the input side of the switch to the output without a specified routing algorithm. In an RNB, a connection request can be made, but existing calls must be rerouted or rearranged to pave way for the new connection request. In WSNB network, a new connection request can be made but a specified routing algorithm must be used in order to avoid blocking in the switch. In a repackable network, any connection is achieved by a repacking algorithm which must ensure that calls are concentrated to some middle stage switch and reduce the load on some other middle stage switches before adding another call to the network [18]. Most of these designs have sought to achieve lower blocking probabilities, increased port count and a lower cross point count within the switch network.

The structure of the TSCN is built based on each of these properties. Since the XBS has been the building block in MIN, it has been studied carefully. In [19], a component efficient design for a parallel optical XBS which utilizes the idle ports as extra input ports and/or output ports was proposed. It was observed that conventional parallel XBSs composed of  $2 \times 2$  BSE have a significant number of idle internal routes between its idle ports. By utilizing its internal idle routes, it reported a one-quarter decreased switch count from  $N^2$  to  $\frac{3}{4}N^2$ . Here, the modified architecture was only applied to single and two stage architectures. Because single stage crossbar switch architectures do not fit dilation as their cross point size increases proportionally to the switch size as  $N^2$ , we focus on applying this to the three stage switch architecture. Also two new design examples were proposed which are; unidirectional and bidirectional. If both are utilized in a proper manner, an architecture with better performing non-blocking properties can be yielded. The concept of idle ports was also applied in [20]. Idle ports of a PILOSS switch were used in bidirectional mode. An Si-wire thermosoptic  $4 \times 4$  PILOSS switch in which a bidirectional use of a single path-independent-insertion-loss switch for polarized

diversity was proposed. The polarized insensitive switching was realized with a single PILOSS switch consisting of  $N^2$  as opposed to  $2N^2$  element switches.

Two principle two-stage switch architectures both composed of two identical optical XBSs with an extra set of input and outputs were proposed in [21]. The cascaded switches based on the utilization of idle ports and idle internal routes in the XBS were reported. The number of cross points, switch control complexities and key optical performances were compared to known cascaded conventional XBS. In [22, 23] a packet based switch which focused on traffic balancing and congestion management was proposed. The switch is called a Clos Unidirectional Network on chip (Clos-UDN). In comparison to the conventional Clos switch, the whole XBS was replaced by a crossbar-like network on chip (NoC) which operates in a unidirectional mode. The proposed multi hop NoC operated as a crossbar with shorter inter router wires than those in a single-hop conventional crossbar. F. Hassen and L. Mhamdi et.al, [24, 25] suggested a three stage clos network which was based on Multi-directional NoC (MDN central modules). Both of these works replaced the conventional crossbars with MDN modules. MDN modules are modified types of UDN switches with their input and output ports operating in multidirectional mode. The NoC based crossbar modules are expensive. To increase the port count, means having larger NoC modules which ultimately increase the cost of designing them. In a white paper of mentor Graphics [26], the creation and simulation of a 2  $\times$  2 optical switch is illustrated. The switch studied employed a double sided mirror whose movement is controlled by an electrostatic, comb drive actuator. A set of folded springs controls the actuator movement. The mirror slides out to the intersection of two perpendicular alignment grooves and then retracts when actuated. Two pairs of optical fiber emitters sits in the alignment groves. In the cross state, the comb drive is actuated and the mirror sits in the groove at the intersection. The mirror reflects the light beam from left input to direct it to the lower output and from the top to the right sides of the switch. In the through state, the comb drive actuates and the mirror retracts. The light beam from left goes straight and is received on the by the output on the right side of the switch. The top input emits the beam to the bottom output. These works report the utilization of the idle ports in a  $2 \times 2$  optical switch. Simulation of this switch was done in S-Edit software to allow for quick assembly.

### 2.1.1 Summary of Contribution

This thesis reports an improved architecture of the TSCN that uses bidirectional XBS. The XBS is modified by utilizing the idle ports. The modified XBSs are applied to the TSCN to form a new architecture. By utilizing the idle ports in the modified XBSs, the non-blocking properties of the new proposed TSCN are investigated through theoretical and computer simulations through examination of additional routes. The total cross point count and the number of rearrangements are also analyzed. This research reports an improved architecture of the TSCN with a reduced number of middle stage switches (figure 9 (a)), reduced cross point count (figure 9(b)) and a reduced number of rearrangements in an RNB clos network. Parallel processing in BNW is investigated and reported with a reduced processing time(figure 9(c)). The reported technique is then applied to a TSCN to come up with a fast parallel algorithm for setting up paths in a TSCN with a component switch size of a power of two. The algorithms for Benes and Clos networks

are both implemented in FPGA. The experimental results of their complexities which highlight the performance of the design in comparison with conventional methods are reported.

(c) Crosspoint complexity reduction

Figure 9: Summary of objectives of proposed target (a) Hardware complexity (b) crosspoint complexity reduction (c) Control complexity

### 2.2 Recent Benes and clos routing control algorithms

#### 2.2.1 Control algorithm in BNW

The BNW is an example of a TSCN. As can be seen in figure 7, the basic building blocks are the 2 × 2 BSEs. It corresponds to the TSCN with n = m = r = 2 and is a RNB network. The BNW provides a unicast connection between N inputs and N outputs where  $N = 2^n$ . The BNW comprises 2n - 1 stages each of which comprises  $N/2 \ 2 \times 2$  switch elements (SE) [27]. There is a total of  $O(N(\log_2 N))$  SEs, which satisfies the theoretical lower bound of the non-blocking switch complexity [28]. Recently, several parallel algorithms have been investigated to apply the BNWs to high-speed time-division multiplexed systems of the agile responsibility to arbitrary permutations [29]. In 1981, Lev et al. formulated parallel algorithms for Benes and Clos networks based on a mathematical graph theory approach [30]. In 1982, Nassimi and Sahni developed a parallel algorithm for BNWs based on an engineering (parallel computing) approach [31]. These works were performed concurrently and independently in these two different approaches. Both achieved a time complexity of  $O((\log_2 N)^2)$  with completely interconnected parallel computers for full permutations with each input corresponding to a unique output. In several practical applications, some inputs and outputs may not have any connection requests (idle state) on them resulting in what is known as a *partial permutation*. In this scenario, original parallel algorithms for BNWs suspend processing when an idle connection is encountered. Parallel algorithms for BNW are required to handle such partial permutations efficiently and effectively [32]. To address this issue, two approaches have been suggested. Firstly, in 1995, Lee and Oruc introduced quadruple datasets to match the idle inputs with idle outputs to act as dummy destinations [33]. Once each input is assigned to a unique output, conventional parallel algorithms are then applied and can therefore work effectively. This approach requires a complicated data structure and a considerable pre-processing time. Secondly, in 2002, Lee and Liew proposed an additional *merging* process which fits in efficiently with the original algorithms [34]. In 2017, the Lee's algorithm was implemented in Field programmable gate array (FPGA) for switch size of N = 8 to 32 by Jiang and Yang [35]. They reported a well-functioning algorithm but it incurred significant overhead time. For the first stage processing of the parallel control unit (PCU) of switch size N = 16, which only required four clocks for completion, they reported that it required up to 17 clocks. Their approach which was based on the crossbar-like centralized architecture resulted in an increased PCU hardware requirement of  $O(N^2)$  [36]. Prior to their implementation of the Lee's algorithm in FPGA, in 2009 Kai et al designed a PCU to configure BNWs. The design only focused on the first stage of the PCU for BNW of switch size  $16 \times 16$  [37]. The approach however employed a distributed architecture rather than a centralized one. This reduced the hardware complexity from  $O(N^2)$  to  $O((\log_2 N)^2)$ . They further suggested that the time complexity can be reduced from  $O((\log_2 N)^2)$  to  $O(\log_2 N)$  using a pipeline architecture suggested by Lee and Oruc. In as much as this algorithm has these advantages, it could not handle partial permutations.

### 2.2.2 Summary of contributions

In this thesis, a parallel algorithm that sets up both full and partial permutations with less overhead time and less additional hardware cost is reported. A PCU with distributed PEs which generates SCB in a pipelined and in part asynchronous manner is constructed in an FPGA.

### 2.2.3 Control algorithms in TSCN

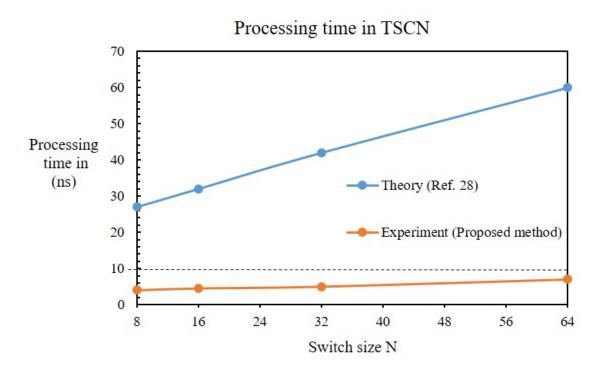

The TSCN requires a setting time of  $O(N \log_2 N)$  under a sequential algorithm [38]. This processing time is too long for its application in data centers and other communication networks. In order to improve the switching time of the TSCN, several parallel algorithms have been proposed. Lev et al. proposed an  $O((\log_2 N)^2)$  algorithm based on the graph theory [30]. Zheng et al. came up with a  $O(\sqrt{N})$  algorithm which was based on a distributed pipeline routing architecture [39]. Most of these algorithms have no reports of implementation in hardware. Besides, the full advantage of the switch having the switch size of the power of two had not been fully taken advantage of in these algorithms. Several parallel routing algorithms for BNW in which the switch size is given by  $N = 2^k$  have already been developed and their hardware implementations in FPGA already reported [37].

### 2.2.4 Summary of contributions

This thesis reports a new parallel routing algorithm for setting up TSCN in which the component switch sizes have a power of two using the above developed BNW for the first time. The algorithm is implemented on an FPGA. The performance of the new algorithm is analyzed and compared with the latest conventional methods.

## Chapter 3

## Design and operation of the proposed structure

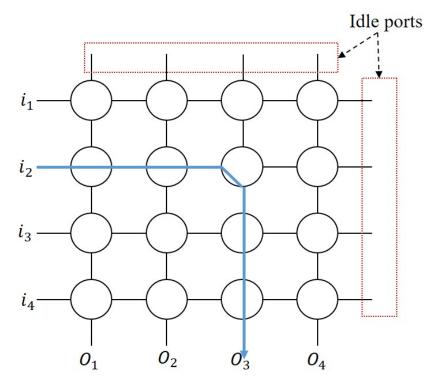

### 3.1 Crossbar modification

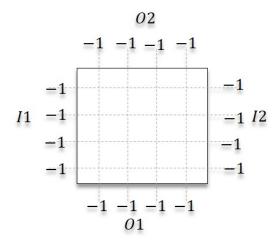

The XBS is made up of  $2 \times 2$  BSE which are either in bar or cross state. To route a call in an XBS as shown in fig. 10, the BSE in the second row and third column must change its state to bar. Recently, a modified XBS switch using idle ports to provide an extra set of input and output reported in [40, 41]. The reported modified XBS single-stage architecture has a drastically reduced cross point count and a simple routing algorithm. The modified XBS is derived from a Conventional XBS which has idle ports on the top and the right side as shown in figure 10.

Figure 10: Conventional crossbar (XBS) Switch with idle ports

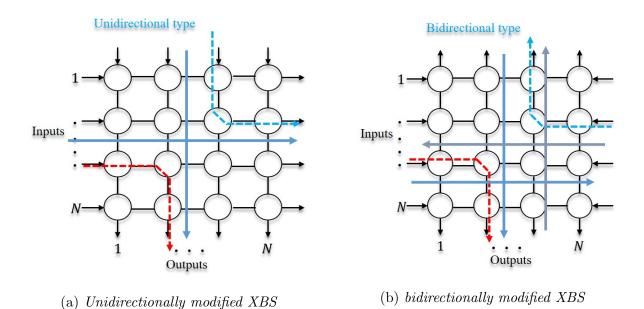

The idea is to utilize these idle ports to provide additional routes in the XBS without increasing the cross point count. Two types of modified XBS one with unidirectional and the other with a bidirectional mode were reported in [21]. These are shown in fig.11.

The unidirectional mode of figure 11 (a) is modified in such a way that the top ports are used as extra inlets and the idle ports on the right are used as extra outlets. The direction of travel of the signal in this switch is such that it moves from left inlets to the right outlets and/or left inlets to right outlets turning to bottom outlets. The signal can also travel from either top to bottom outlets or from top towards bottom and turning to the right outlets. This is considered as unidirectional switch because its either left to

Figure 11: Two possible types of XBS modification (a) Unidirectional modified (b) bidirectionally modified

right or top to bottom or left to right going bottom or top to bottom going right. The bidirectional one shown in figure 11 (b) is modified by using the right side idle ports of the XBS as inlets and the top ones as outlets. Signals can travel from left towards right turning to the lower outlets and can also travel from the right side going towards left turning to the upper outlets. Because of this direction of travel in both right and left directions by two different signals, this switch is referred to as *bidirectional switch*. These two types of XBS are applied to the TSCN in order to provide additional internal routes without increasing the size of XBS which, in turn yields a smaller number of XBSs, reduced cross points and a reduced number of rearrangements in RNB switches.

## 3.2 Application of XBS to TSCN

The modified XBSs are used to design a new TSCN architecture. Firstly, a special case of a bidirectional modified TSCN is described in which the number of rearrangements are reduced to only one regardless of n, m and r at a negligible cost of extra crosspoints. The non-blocking properties of the TSCN such as the SNB, WSNB and RNB depend on the number of middle stage switches m. It has been observed that by adjusting this parameter appropriately, the properties of the TSCN are also changed. The proposed design reported in this thesis focuses mainly on the middle stage XBSs.

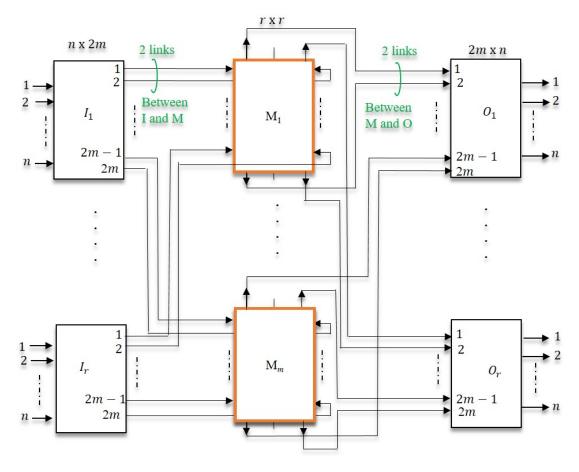

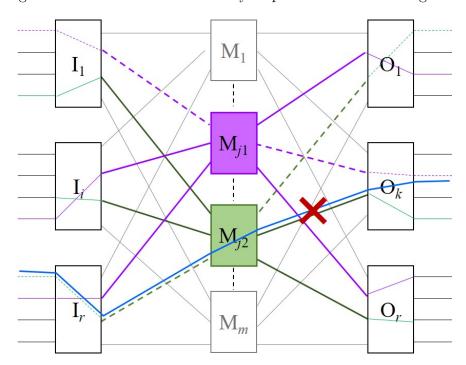

### 3.2.1 Bidirectional TSCN

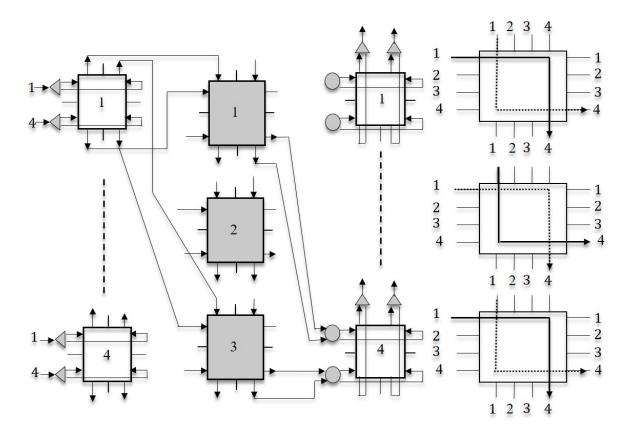

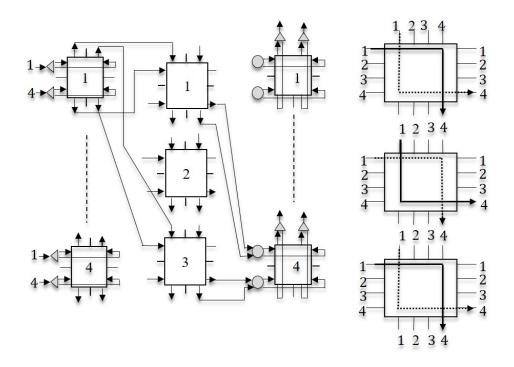

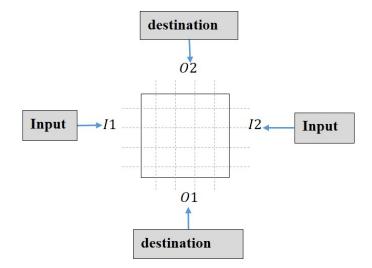

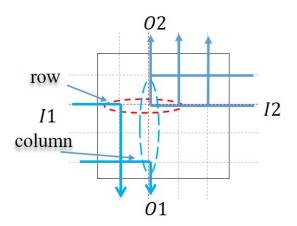

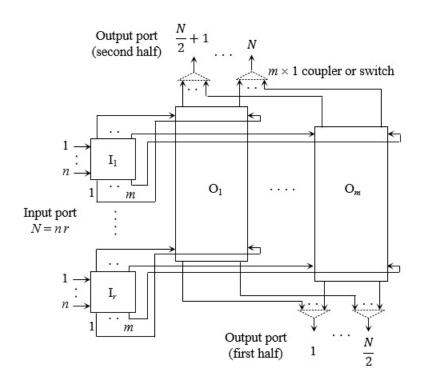

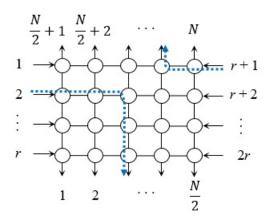

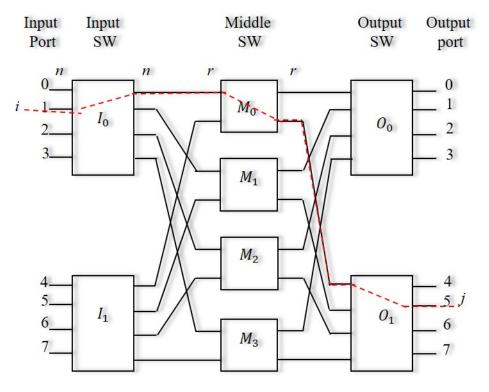

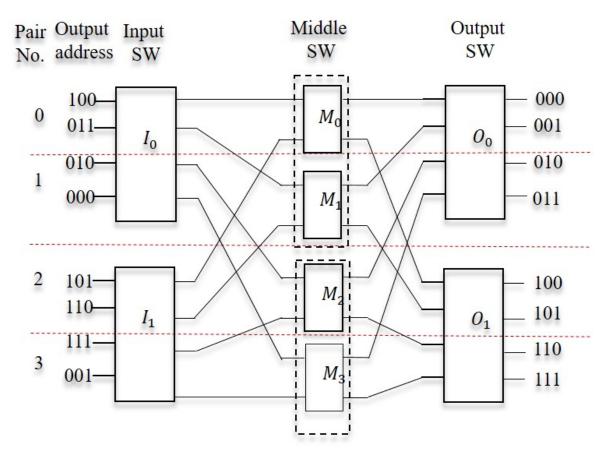

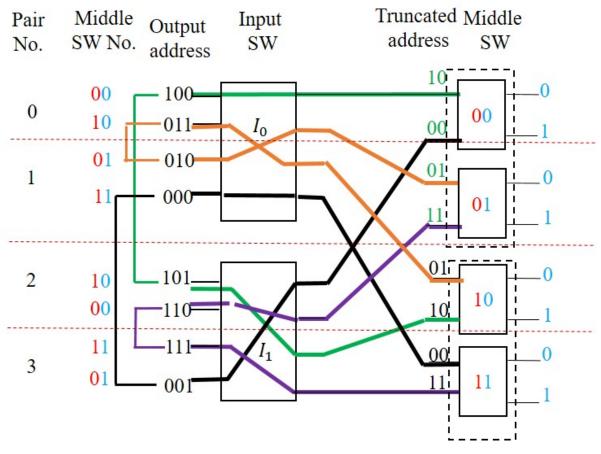

The proposed general architecture of the modified TSCN using modified XBS is as shown in figure 12 below. The proposed architecture has three stages similar to the conventional TSCN. Each stage is composed of XBSs represented by  $I_x$ ,  $M_y$  and  $O_z$  with  $(1 \le x \le r, 1 \le y \le m, 1 \le z \le r)$ . The input stage XBS  $I_x$   $(1 \le x \le r)$  are  $n \times 2m$  ordinary XBS and its outputs 2m - 1 and 2m are connected to the left and right side of the middle stage XBS respectively. Similarly, the third stage also is composed of  $2m \times n O_z$  XBS. Their inputs 2m - 1 and 2m may simultaneously receive signals from the middle stage switches. The total number of cross points in the input and output stages become twice as large as the conventional TSCN. However, the number of middle stage switches is reduced drastically. The middle stage has  $r \times r$  bidirectional XBS with extra sets of r inlets and r outlets. It should be stressed here that each of the first stage  $I_x$  XBS provides two links to each of the rows of every  $M_y$  middle stage XBS. The columns of a modified XBS are used as outputs and feed to the inputs of the XBS in the next stage. The proposed structure also provided two links from each of the  $M_y$  to each  $O_z$ . For example, two signals from  $I_r$  can both be routed through the M1 XBS to any two third stage XBSs. The two signals may simultaneously coexist in a single row of middle stage XBS. In a conventional TSCN, only a single link is provided between each switch in each stage.

Figure 12: Two possible types of XBS modification

The utilization of idle ports introduces additional routes and therefore more than one signal from each XBS in one stage can be routed to another XBS in another stage. The other special design is as shown in figure 13. In this design the middle stage is composed of m = n modified XBS used in bidirectional mode. Each first stage is composed of ordinary  $r \ n \times n$  XBSs. Each of the output from the first stage is fed either to the left or right inlet of the middle stage switch through a

$1 \times 2$  switch. At the second stage, it is switched to the third stage from the top outlets of the switch. The wiring pattern of the inlets at the left side and outlets at the bottom

sides is the same as that in a conventional XBS of the TSCN.

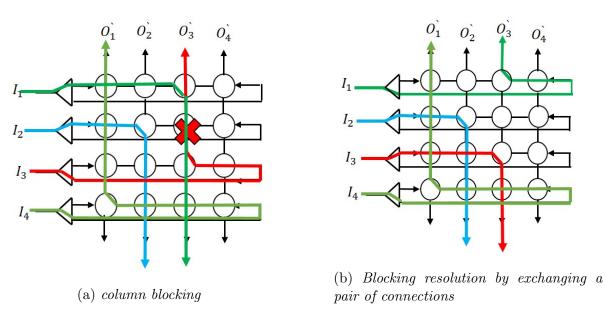

Figure 13: Special configuration with m = n middle stage switches

The signals are then fed to the third stage switches through a  $2 \times 2$  BSE. As a result of the  $1 \times 2$  switch in the first stage, only a single connection request from the first switch in the first stage to the first middle stage switch occupies a row of the middle stage switch although it has two inlets at the end of each of its rows. Therefore, only a single signal is allowed to travel along the row of the middle stage switch either from the left side going right or entering to the right side going left. This prevents row blocking from occurring in any row of the second stage of the TSCN. However, blocking can occur when two input signals from different input switches are destined for an identical switch. As can be seen when the signal indicated in blue seeks to connect to the upper side in the first column, blocking may occur with the green signal which is already destined for the bottom output in the same column. This is further illustrated in figure 14a, i.e., if a signal from a lower input switch on inlet I3 is fed to the right side, and its destination is  $O'_3$ , we see that blocking can occur in the column since another signal from input switch on inlet I1 is already occupying the column. This is known as column blocking. As can be seen in figure 14b, this kind of blocking can easily be resolved by exchanging a pair of routes to other switches after a conventional rearrangement control. The blocking that occurs here is resolved by diverting the existing connection to an alternate route through the same column swapping only a single pair of routes. This limits the number of rearrangements in the proposed  $C_{\rm B}(n,n,r)$  to only a single rearrangement. Therefore it requires at most a single rearrangement regardless of n or r. therefore the number of rearrangements  $R_B(n, n, r)$  is expressed as

$$R_B(n,n,r) = 1 \tag{1}$$

Figure 14: Column Blocking and blocking resolution

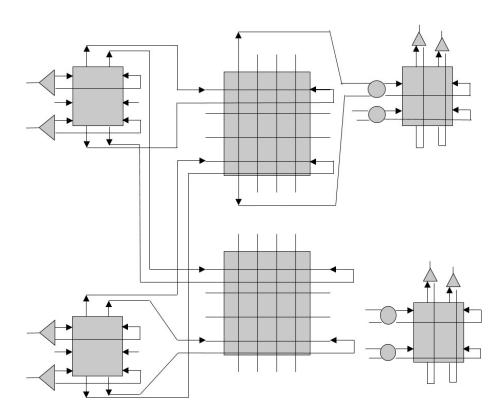

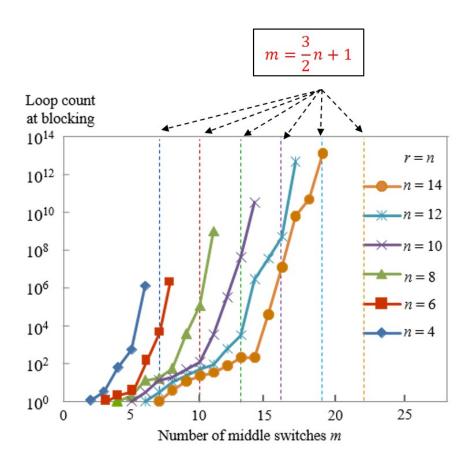

The second case of the bidirectional TSCN has a reduced number of middle stage switches. In this design (figure 15), Each input to the first stage-switches  $I_x$  has a  $1 \times 2$ switch to route the signal either to the left or to the right side of the switch. The extra unused ports on the right side of the switch are used as extra inlets and the top ports as extra outlets. The output signal of the first stage switches is tapped from either the top or the bottom depending on the side the signal entered from. The signal entering through the left side of the XBS can travel to the bottom outlet while the signal entering through the right side can travel to the upper outlet. A pair of column outlets of the first stage are fed to the same row of each of the second stage switches. The upper outlet is fed to the left side of the middle stage XBS and the bottom outlet to the right side of the middle stage switch. Similarly, the column outlets of the second stage switches are fed to the third stage switches through  $2 \times 2$  BSE which distributes and exchanges the signal in the third stage. In the third stage, the output ports are equipped with  $2 \times 1$ BSE to select the appropriate route from where the signal is emanating. The use of idle ports in this proposed design allows each of the first stage switches to route at most two signals to the same middle stage switch.

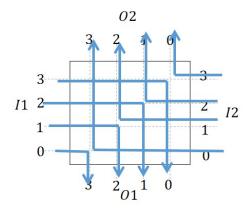

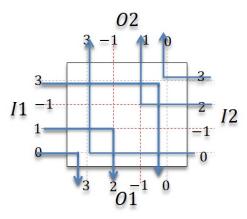

Consider a conventional TSCN C(n, m, r) with n = 4, m = 4 and r = 4. In this switch, we require a minimum of m = n = 4 middle stage switches to connect all n = 4inputs from a single XBS, i.e. for the switch to maintain RNB properties. Since blocking has been avoided in the first and third stages, we focus mainly on the routing of calls in the middle stage switches only. This premise is also based on a well-known fact that the properties of the TSCN is mainly dependent on the middle stage switches. In a conventional TSCN, two calls from the same first stage switch cannot be switched to the third stage through the same middle stage XBS. We also see that two calls originating from two different first stage switches need at least two rows and two columns in a single middle stage XBS to be switched to the third stage. This means a total of 2 rows and 2 column resources are used up in a single XBS to route two calls as can be seen in Fig. 16(a). The bidirectional TSCN represented by  $C_B(n, m, r)$  allows for two calls coming from the same input stage XBS to be routed to the third stage through the same middle

Figure 15: bidirectional modified TSCN with  $1^{st}$  and  $3^{rd}$  stage modified

stage XBS because it has additional inlets and outlets. Two calls from two different first stage switches headed for the same destination switch in the third stage can use two different rows but will share a column. This will use up 2 rows and a single column (3 resources) (see Fig. 16b). Similarly, two calls coming from the same first stage switch can share a row to reduce the resource requirement to 3 resources (see Fig. 16 c). A special case where two calls from the same first stage switch headed for the same third stage switch will share a row and a column resulting only in using 2 switch resources (see Fig. 16d).

Figure 16: Sharing of rows and columns by a pair of connections in XBS

Let us see how the sharing of rows and columns in the proposed TSCN  $C_B(n, m, r)$  allows routing n = 4 inputs through m < n. Consider routing all calls from the first stage switch to the last switch of the last stage i.e. input SW 1, 2, 3, 4 to output SW 4, 3, 2, 1 respectively.

Figure 17: Routing n calls using m < n middle stage switches

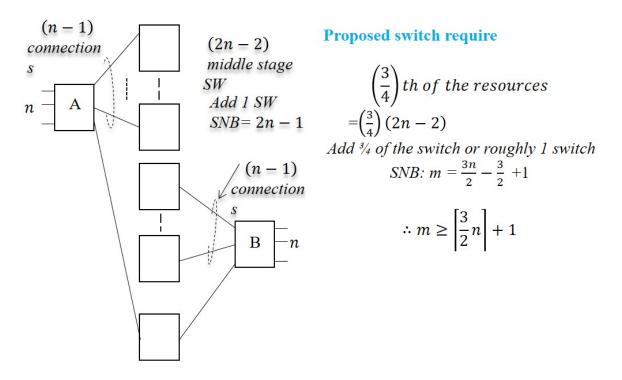

As can be seen in figure 17, the first n-1 calls can be routed through the first three middle switches. The remaining call can be routed through any of the available routes indicated by dotted lines in any of the three middle stage switches shown on the right side. The above demonstrates that to route n = 4 inputs from any first stage switches, a minimum of 3 middle stage switches is required. The conventional TSCN requires a minimum of 4 middle stage switches to route n = 4 from each of the first stage XBS. It has also been demonstrated that the row/column resource usage reduces to three quarters. Though the conventional TSCN requires 4 row/column resources, based on the above, we hereby make a proposition that the minimum number  $m_L$  of middle stage switch resources required to route n inputs of each of the first stage XBS becomes as follows:

$$m = \left\lceil \frac{3n}{4} \right\rceil \tag{2}$$

for the bidirectional TSCN. The |x| denotes the ceiling function which is to say the value of the least integer greater than or equal to x.

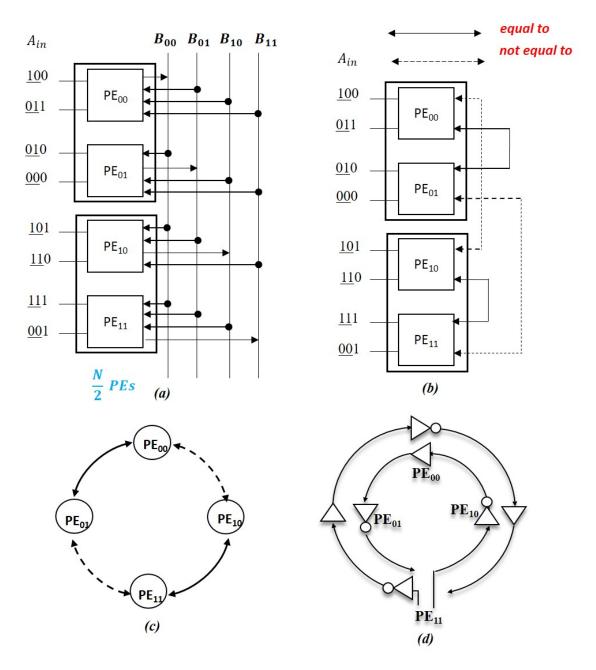

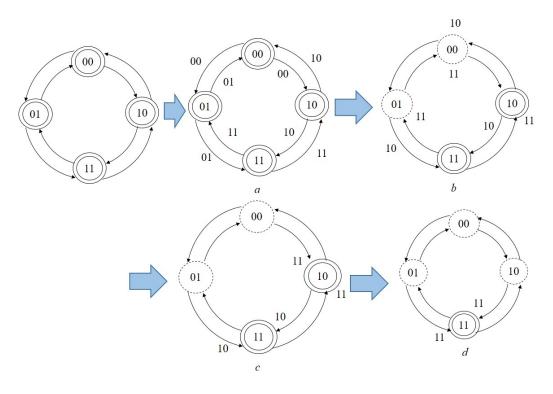

### 3.3 Proposed Unidirectional TSCN